Aprende a tu Ritmo: Estructura de Código VHDL

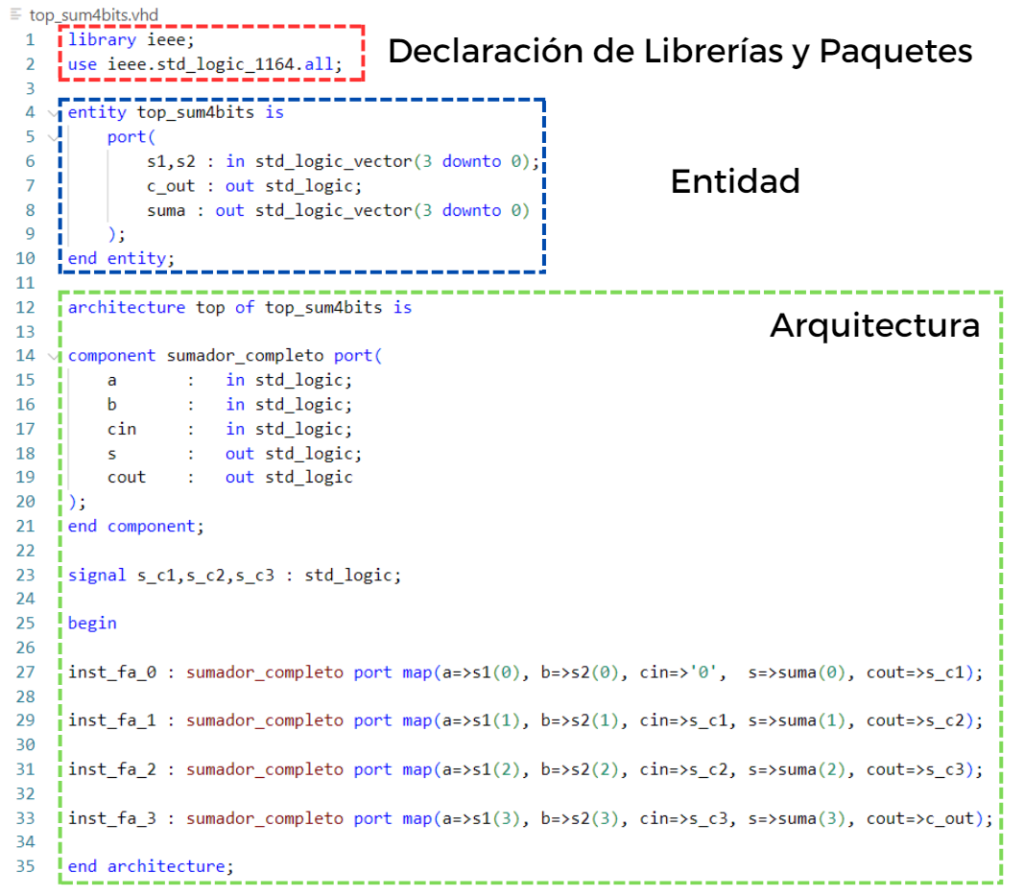

Un código en VHDL se compone de una conjunto de unidades de diseño. Para que este código sea sintetizable se necesita al menos dos unidades de diseño: una declaración de entidad y un cuerpo de arquitectura asociado a la entidad. El esqueleto de un programa VHDL típico puede explicarse mejor mediante un ejemplo.

Declaración de Librerías y Paquetes

En la primera sección de código VHDL se declara las librerías a utilizar y se importan los paquetes requeridos de estas Librerías.

Los paquetes contienen funciones, procedimientos, componentes, constantes y tipos de datos. Si algún tipo de información (código) se utiliza continuamente, se recomienda colocar dentro de una librería y de esa manera reusar el código de manera más eficiente.

Se cuentan con dos Librerías principales: Librería IEEE y Librería STD

La librería IEEE (Institute of Electrical and Electronics Engineers) y se utiliza para incluir paquetes que contienen definiciones estándar para tipos de datos, operaciones y funciones comunes que son utilizadas en el diseño digital.

| Librería | Paquete | Es requerido declararla? |

|---|---|---|

| IEEE | std_logic_1164 | Si, es requerido declararlo |

| STD | standard | No es requerida su declaración |

Entre los paquetes más utilizados podemos encontrar:

- Paquete standard: Contiene la definición de varios tipos de datos y varias operaciones lógicas.

- Paquete textio: Permite el manejo de textos y archivos.

- Paquete std_logic_1164. Define nueve valores para los tipos de datos STD_LOGIC (similar a bit) y STD_LOGIC_VECTOR (similar a bit_vector).

Tambien existen paquetes muy útiles:

- Paquete numeric_std. Introduce los tipos SIGNED y UNSIGNED junto con sus operadores, teniendo como base el tipo de dato STD_LOGIC. Admite tipos de datos con y sin signo. Se trata de subtipos de std_logic_vector con operadores sobrecargados que permiten utilizarlos como vectores de valores lógicos y como números binarios (en representaciones de complemento a dos con signo o sin signo). Además los operadores aritméticos estándar (+, -, *, /, **, >, <, <=, >=, =, /=) pueden aplicarse a señales de tipo con o sin signo.

| signed() | Convierte un tipo de dato std_logic_vector/unsigned a signed |

| unsigned() | Convierte un tipo de dato std_logic_vector/signed a unsigned |

| std_logic_vector() | Convierte un tipo de dato singed/unsigned a std_logic_vector |

| to_integer() | Convierte un tipo de dato signed/unsigned a integer |

| to_signed() | Convierte un tipo de dato integer a signed |

| to_unsigned() | Convierte un tipo de dato integer a unsigned |

- Paquete std_logic_unsigned. Introduce funciones que permiten operaciones aritméticas, corrimientos y comparación con señales de tipo STD_LOGIC_VECTOR que actúan como números sin signo.

- Paquete std_logic_signed. Las misma funcionalidad que en el caso anterior pero sobre señales STD_LOGIC_VECTOR que actúan como números con signo.

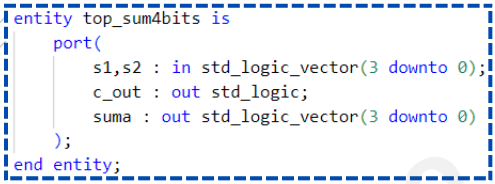

Entidad

La parte principal de una entidad (ENTITY) es PORT, que es una lista de especificaciones de todos los puertos de entrada y salida del circuito.

Se declaran dos entradas de 4 bits s1, s2 de tipo std_logic_vector y dos salidas, c_out de tipo std_logic que es de un bit y suma de tipo std_logic_vector que es de 4 bits.

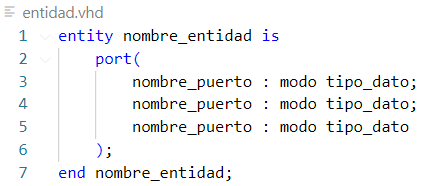

La sintaxis simplificada de una declaración de entidad es

La declaración de puertos se compone del nombre_puerto, modo y tipo_dato. El término modo indica la dirección de la señal, que puede ser in, out y inout, representando entradas, salidas o bidireccional respectivamente. Las palabras clave in y out indican, respectivamente, que la señal fluye «hacia» y «fuera» del circuito. Representan el hecho de que el puerto correspondiente es una entrada o una salida del circuito. La palabra clave inout indica que la señal fluye en ambas direcciones y que el puerto correspondiente es un puerto bidireccional.

El nombre de la entidad (nombre_entidad) puede ser cualquiera palabra excepto las palabras reservadas de lenguaje.

- Todos los miembros del campo port de la sintaxis antes mostrada son señales. Es decir, cables que entran y salen del circuito.

- Los puertos pueden ser in (entrada), out (salida) y inout (entrada/salida).

- El tipo de señal puede ser integer, std_logic, std_logic_vector, unsigned, signed, entre otros.

Arquitectura

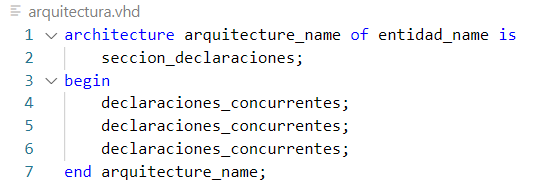

En la arquitectura se especifica el funcionamiento interno del circuito. En VHDL, podemos desarrollar múltiples arquitecturas para la misma declaración de entidad y posteriormente elegir una para enlazar con la entidad para simulación o síntesis. La sintaxis simplificada de una arquitectura es:

- La arquitectura (arquitecture) tiene dos partes: un parte declarativa (opcional) y otra de sentencias que inician a partir de BEGIN.

- La parte declarativa puede contener las siguientes declaraciones: tipos, señales, variables, archivos, atributos, entre otros.

- La parte de las declaraciones_concurrentes son donde las sentencias VHDL (código) se colocan.

- El nombre de la arquitectura puede ser cualquiera (excepto las palabras reservadas por el lenguaje), incluso el mismo nombre de la entidad.

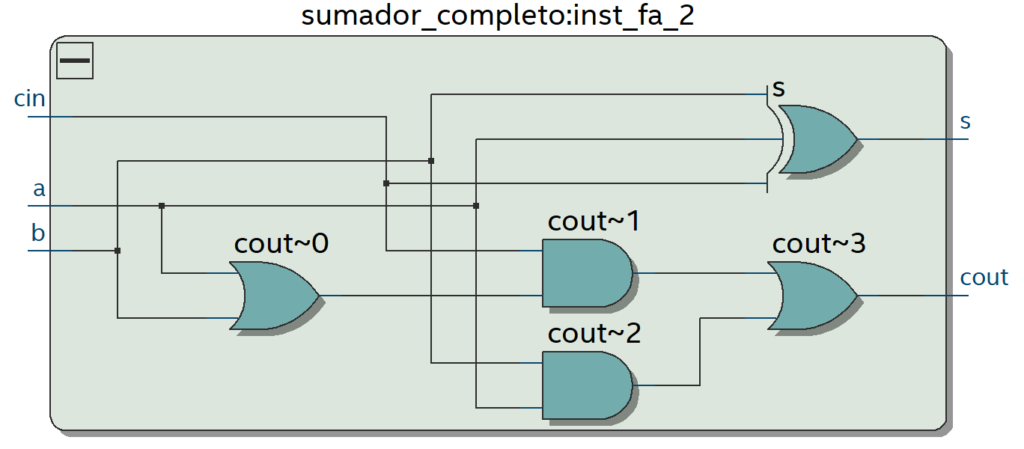

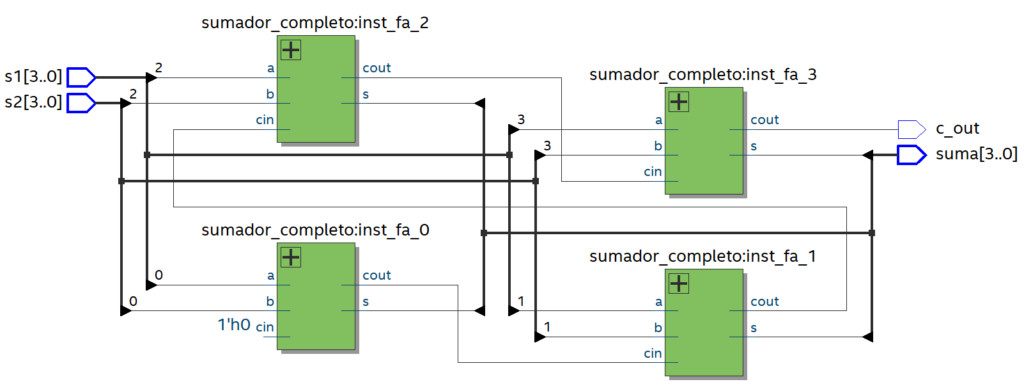

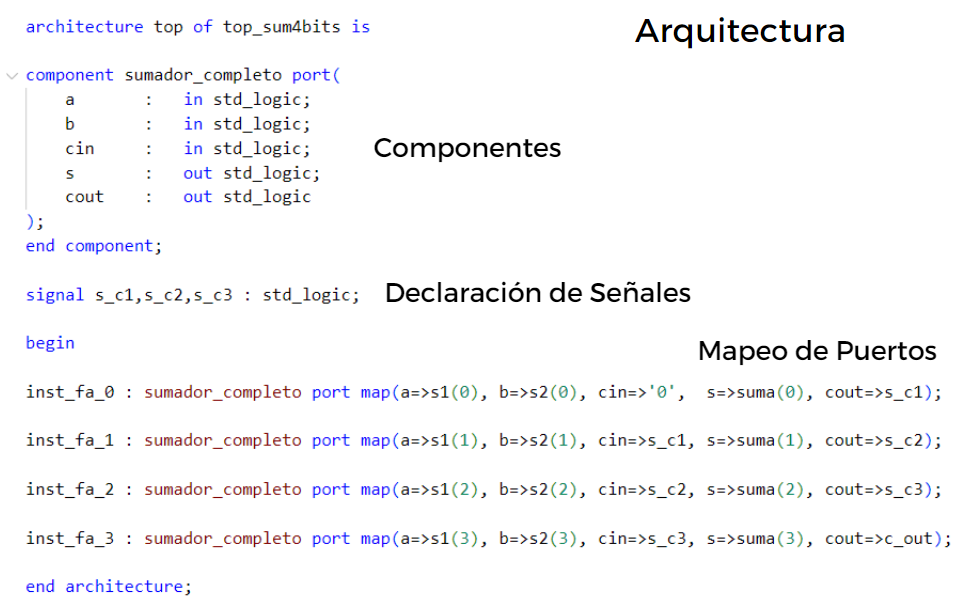

En la arquitectura del ejemplo top_sum4bits se realiza la declaración del componente sumador_completo, declaración de señales auxiliares para su posterior mapeo realizado luego de la palabra clave begin. El circuito es sintetizado usando Quartus y se obtiene la siguiente netlist: