Aprende a tu Ritmo: Process en VHDL

¿Qué es un proceso en VHDL?

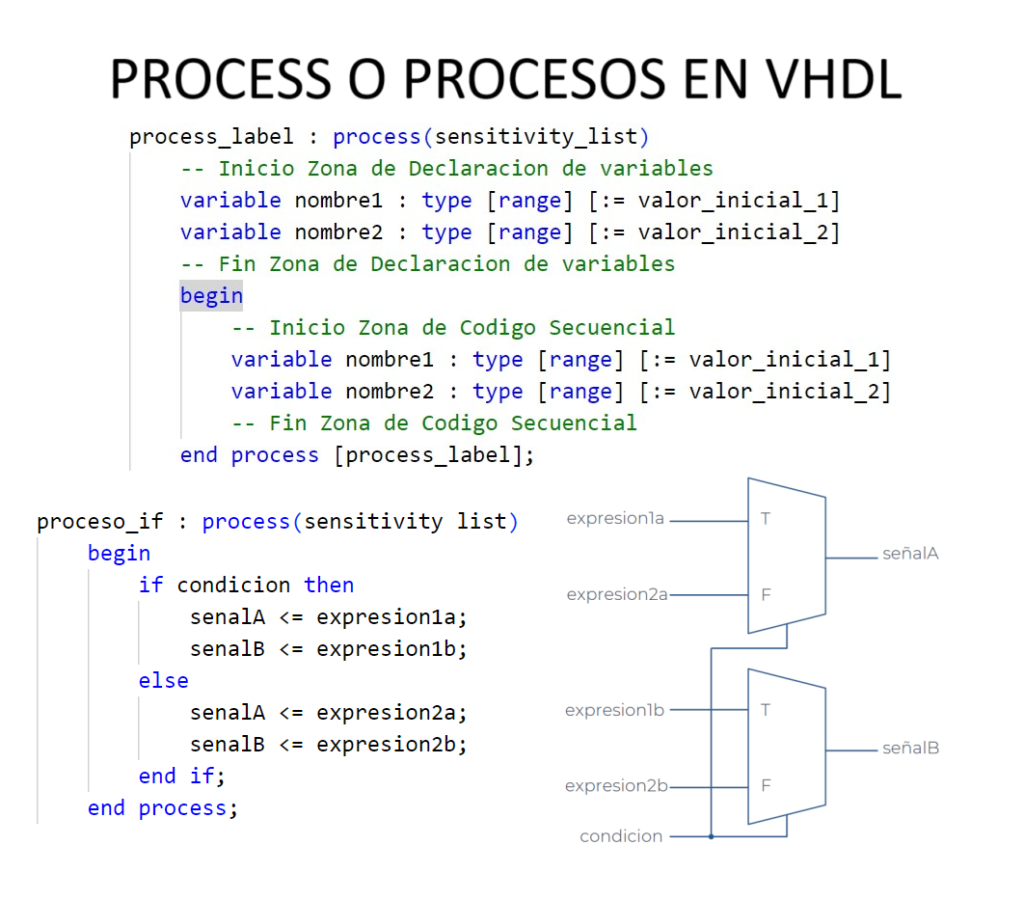

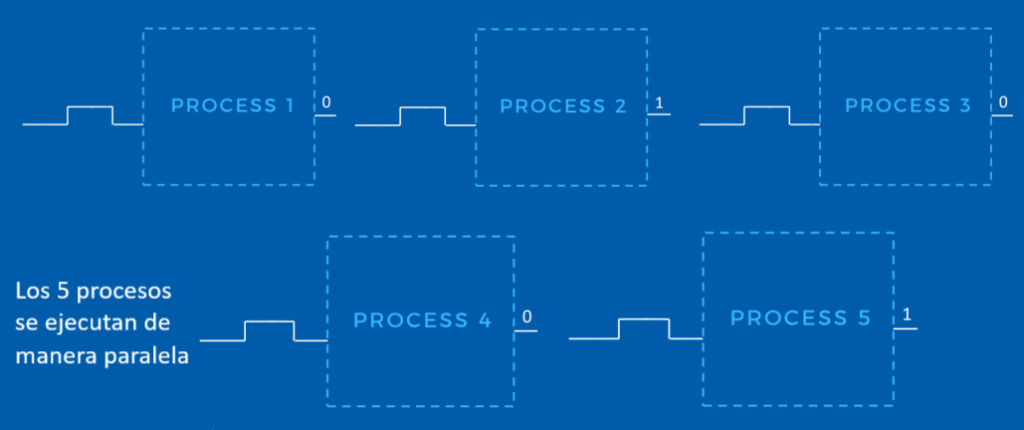

Un process o proceso es un bloque de código en el cual de manera similar a los lenguajes de programación, el código dentro de este bloque es ejecutado de manera secuencial. Los procesos son declarados en la sección concurrente de una arquitectura y por ello diferentes procesos son ejecutados de manera paralela.

El bloque process se utiliza comúnmente para describir la lógica combinacional o secuencial en un diseño digital. Puede contener declaraciones de señales, variables, operaciones aritméticas, comparaciones, y otros elementos que definen el comportamiento del circuito. En combinación con las declaraciones if, case, for, y otras, el process se convierte en una herramienta versátil para describir el comportamiento de circuitos digitales.

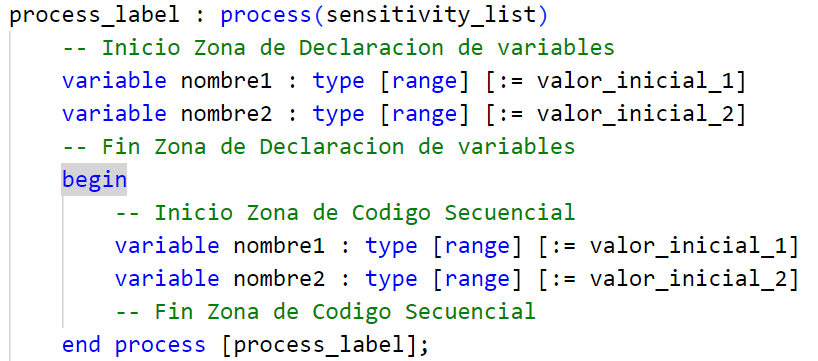

Sintaxis del Process:

La etiqueta del proceso es opcional, pero es recomendado utilizar etiquetas para poder tener un código más claro y entendible.

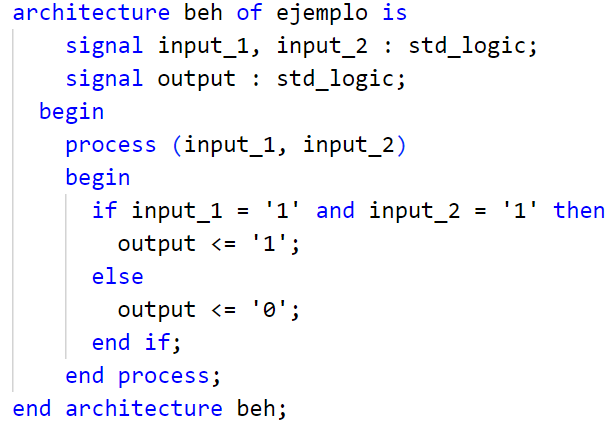

En este ejemplo, el process se sensibiliza a los cambios en las señales input_1 e input_2. Cuando hay un cambio en alguna de estas señales, el código dentro del process se ejecuta y actualiza la señal output según la lógica definida.

Lista de Sensibilidad

En VHDL, la lista de sensibilidad, también conocida como «sensitivity list», especifica las señales a las que un proceso está «sensibilizado». La sensibilidad indica cuándo debe ejecutarse el bloque de código dentro del proceso. En otras palabras, el proceso se ejecutará cuando ocurra un cambio en cualquiera de las señales mencionadas en la lista de sensibilidad.

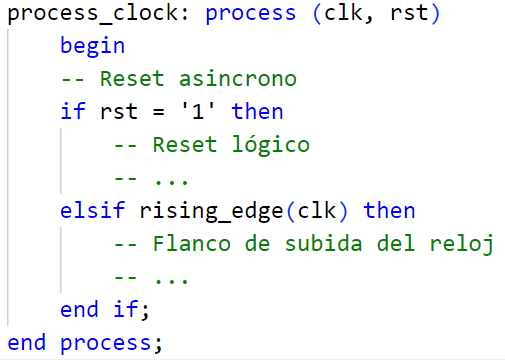

La lista de sensibilidad se coloca entre paréntesis junto a la palabra clave process.

En este ejemplo, el proceso está sensibilizado a las señales clk y rst. Esto significa que el bloque de código dentro del proceso se ejecutará cuando haya un cambio en cualquiera de estas señales. La sensibilidad a rising_edge(clk) asegura que el proceso solo se ejecute en el flanco de subida del reloj.

Es importante tener en cuenta que no todos los procesos en VHDL requieren una lista de sensibilidad. Por ejemplo, los procesos que describen lógica combinacional a menudo no necesitan una lista de sensibilidad, ya que se ejecutan cada vez que cualquiera de las señales en su cuerpo cambia. Sin embargo, para los procesos que describen lógica secuencial o dependen de eventos específicos, la lista de sensibilidad es crucial para definir cuándo deben ejecutarse.

Recomendaciones para circuitos combinacionales con procesos asíncronos

Usando procesos podemos describir circuitos combinacionales y secuenciales. Los circuitos combinacionales pueden ser considerados circuitos asíncronos, por lo que hablamos de procesos asíncronos.

Debemos tener en cuenta lo siguiente:

- Todas las entradas del circuito deben colocarse en la lista de sensitividad.

- Al utilizar sentencias secuenciales como if-then-else o case-when, se deben incluir todas las asignaciones necesarias para cubrir todos los casos posibles que puedan presentar las entradas.

- Un proceso debe describir una única parte del circuito. Si en el diseño se ha elegido que el bloque A sea descrito por un proceso, este solamente debe describir el bloque A.

Recomendaciones para circuitos combinacionales con procesos síncronos

Para describir circuitos secuenciales, se requieren definir elementos de memoria y bloques sincronizados. El uso más frecuente y preferido para describir estos circuitos es el de procesos síncronos.

Debemos tener en cuenta lo siguiente:

- Definir correctamente cuales de las señales son síncronas y cuales son asincronas.

- Todas las señales asíncronas y la señal de reloj deben incluirse en la lista de sensitividad, las síncronas no son necesarias de incluirlas.

- Saber ubicar el dominio de reloj dentro del proceso. Las señales síncronas deben estar dentro de esta zona y las asíncronas fuera.