Python vs Verilog: Procesamiento de Imágenes en Tiempo Real

⚙️ Dos enfoques, un mismo problema

El procesamiento de imágenes es una tarea clave en múltiples aplicaciones industriales y tecnológicas: visión artificial, inspección automatizada, sistemas embebidos, robótica, entre otros.

Sin embargo, aunque el problema a resolver sea el mismo —procesar una imagen—, el enfoque utilizado puede cambiar radicalmente el rendimiento del sistema.

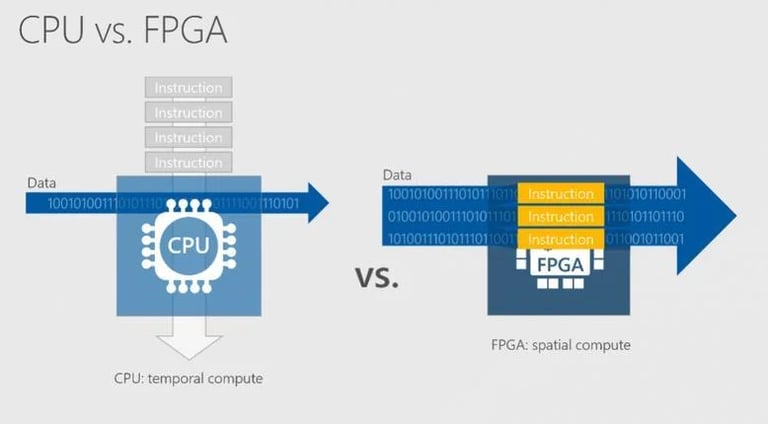

En este contexto, Python y Verilog representan dos paradigmas completamente distintos:

Python → procesamiento en software ejecutado en CPU

Verilog → procesamiento en hardware implementado en FPGA o ASIC

Comprender esta diferencia no es solo un tema académico, sino una decisión crítica en el diseño de sistemas de alto desempeño.

⚙️ Python: un vistazo desde el procesamiento en software

Python es uno de los lenguajes más populares en la actualidad debido a su facilidad de uso, versatilidad y amplio ecosistema de librerías.

En el campo del procesamiento de imágenes, permite:

Aplicar filtros y transformaciones complejas

Trabajar con librerías especializadas como OpenCV

Desarrollar soluciones rápidamente

No obstante, para entender claramente sus limitaciones frente a hardware, en este artículo se utiliza un enfoque deliberadamente básico: procesamiento mediante bucles (for).

Ejecución secuencial y cuello de botella

Cuando procesamos una imagen en Python:

Se lee la imagen

Se recorre pixel por pixel

Se aplica una operación (como un filtro)

Se escribe el resultado

Cada uno de estos pasos se ejecuta como instrucciones en la CPU, de manera secuencial.

Esto implica que:

Cada operación depende de la anterior

No existe paralelismo real (en este caso)

El rendimiento queda limitado por la frecuencia del procesador

Aunque existen técnicas avanzadas como multiprocesamiento o vectorización, en este análisis se omiten intencionalmente para evidenciar la diferencia fundamental con hardware.

⚙️ Verilog: implementación de hardware para procesamiento de imágenes

A diferencia de Python, Verilog no describe instrucciones que se ejecutan, sino circuitos que existen físicamente.

Esto cambia completamente la forma de abordar el problema.

En lugar de ejecutar operaciones paso a paso, el hardware permite:

Procesamiento paralelo

Ejecución simultánea de múltiples operaciones

Alta velocidad determinística

Una de las preguntas más comunes cuando se inicia en diseño digital es:

¿Cómo representamos una imagen dentro de hardware?

Durante la etapa de simulación, Verilog permite cargar archivos de datos mediante instrucciones como:

$readmemb

$readmemh

Estos archivos pueden tener formatos como:

.mem

.hex

.txt

En esencia, contienen datos binarios que representan la imagen.

¿Cómo se carga una imagen en un sistema digital?

Representación de un pixel en memoria

Considerando un pixel en formato RGB de 24 bits:

8 bits → Rojo

8 bits → Verde

8 bits → Azul

Ejemplos:

Rojo → 11111111 00000000 00000000

Amarillo → 11111111 11111111 00000000

Cada línea del archivo de memoria representa un pixel.

Por ejemplo:

Imagen Full HD (1920x1080)

→ 2,073,600 líneas de datos

Es importante distinguir dos etapas fundamentales:

Simulación

Los datos se cargan como variables

Se leen secuencialmente en el testbench

Síntesis

Los datos se mapean a memoria física (ROM)

Se accede mediante direcciones

Arquitectura típica:

memory_address → dirección de memoria

RGB_in → salida de datos

Diferencia entre simulación y síntesis

⚙️ El filtro de Sobel

El filtro de Sobel es un operador utilizado para detectar bordes en imágenes.

Se basa en una operación conocida como convolución.

Consiste en:

Tomar una ventana (kernel)

Multiplicarla por una región de la imagen

Obtener un valor de salida

En este caso se utiliza un kernel de 3x3.

¿Qué es la convolución?

Componentes del filtro

Gx → detecta cambios en columnas (bordes verticales)

Gy → detecta cambios en filas (bordes horizontales)

La combinación de ambos permite obtener una imagen donde los bordes son claramente visibles.

⚙️ Implementación del filtro en Python

La implementación se realiza usando estructuras básicas:

Bucles for

Acceso directo a píxeles

Este enfoque refleja cómo la CPU ejecuta instrucciones simples.

Resultado de rendimiento

Para una imagen de 1920x1080:

⏱ Tiempo de ejecución: 9.37 segundos

Esto evidencia el costo de la ejecución secuencial.

⚙️ Implementación en Verilog (simulación)

En este caso no se implementa directamente el hardware físico, sino su simulación en ModelSim.

Aun así, el comportamiento refleja cómo se ejecutaría en hardware.

Resultado

⏱ Tiempo: ~10 ms (9946120 ns)

⚙️ Comparativa final

👉 Diferencia: ~1000x

⚙️ Reflexión final

Este resultado no significa que Python sea “peor”.

Significa que:

Cada herramienta tiene su contexto

El hardware es clave cuando se requiere tiempo real

🚀 Lleva el procesamiento de imágenes al siguiente nivel

Si quieres entender cómo pasar de software a hardware y diseñar sistemas de alto rendimiento, estos temas son el siguiente paso:

👉 Continúa aprendiendo:

Process en VHDL

ModelSim: simulación de hardware

Instalación de Quartus Prime Lite

Estos conceptos son clave para implementar procesamiento en tiempo real sobre FPGA.

Accede a nuestro curso de FPGA y empieza desde cero

🌐 (link a /curso-fpga)

Descubre nuestras soluciones de automatización industrial

🌐 (link a /automatizacion-industrial)