Process en VHDL: Fundamentos para Diseño Digital

⚙️ Introducción: más allá de escribir código

Cuando se comienza a trabajar con VHDL, uno de los conceptos que genera mayor confusión es el bloque process.

Esto ocurre porque, a primera vista, su comportamiento parece similar al de un lenguaje de programación tradicional. Sin embargo, VHDL no describe software, sino hardware, y esta diferencia cambia completamente la forma en que debemos entender su ejecución.

⚙️ ¿Qué es un process en VHDL?

Un process es un bloque de código que se ejecuta de forma secuencial internamente, pero que existe dentro de un entorno concurrente.

Esto significa:

Dentro del process → las instrucciones se ejecutan en orden

Entre procesos → se ejecutan en paralelo

Este modelo híbrido es fundamental para describir circuitos digitales de manera precisa.

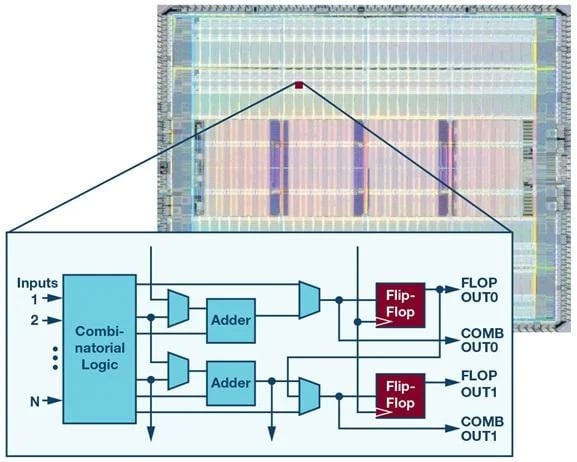

⚙️ Uso del process en diseño digital

El bloque process se utiliza para describir:

Lógica combinacional

Lógica secuencial

Operaciones aritméticas

Comparaciones

Control de flujo (if, case, loops)

Gracias a esto, el process se convierte en una herramienta extremadamente versátil en el diseño digital.

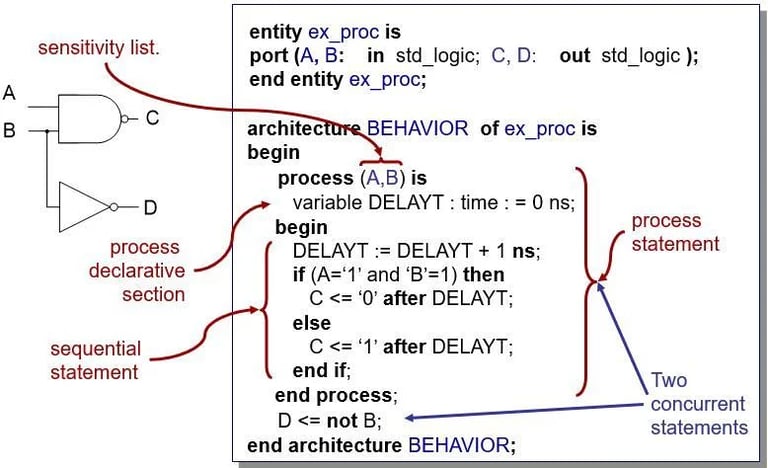

⚙️ Sintaxis del process

Aunque la etiqueta del process es opcional, su uso es altamente recomendado para mejorar la legibilidad del código.

Un process se declara dentro de la arquitectura y puede incluir:

Señales

Variables

Operaciones

Estructuras de control

⚙️ Lista de sensibilidad (Sensitivity List)

La lista de sensibilidad define cuándo se ejecuta el proceso.

Ejemplo típico:

process(clk, rst)

Esto significa que el process se ejecuta cuando:

Cambia el reloj

Cambia el reset

Ejecución controlada por eventos

En diseños síncronos es común utilizar:

rising_edge(clk)

Esto asegura que el proceso se ejecute únicamente en el flanco de subida del reloj.

⚙️ Procesos combinacionales (asíncronos)

Los procesos combinacionales describen lógica que depende directamente de sus entradas.

Recomendaciones clave

Incluir todas las entradas en la lista de sensibilidad

Cubrir todos los casos posibles en estructuras condicionales

Evitar inferencia de latches

Mantener un process por bloque lógico

⚙️ Procesos secuenciales (síncronos)

Los procesos secuenciales describen circuitos con memoria:

Flip-flops

Registros

Contadores

Recomendaciones clave

Definir correctamente señales síncronas y asíncronas

Incluir señales asíncronas (reset) en la lista

Ubicar correctamente el dominio de reloj

Encapsular lógica dentro del evento de reloj

⚙️ Buenas prácticas de diseño

Un uso incorrecto del process puede generar:

Comportamientos no deseados

Problemas en síntesis

Diferencias entre simulación y hardware

Por ello, es fundamental:

Entender su semántica

Mantener consistencia en el diseño

Validar mediante simulación

🧠 Domina la lógica antes de escalar tu diseño

Si quieres fortalecer tu base en VHDL y evitar errores comunes en hardware, continúa con:

👉 Continúa aprendiendo:

Una base sólida te permitirá diseñar sistemas más robustos y escalables.

🚀 Aprende VHDL con enfoque práctico

Acceder al Curso de FPGA → /curso-fpga

🔧 Descubre nuestras soluciones de automatización industrial

Ver soluciones → /automatizacion-industrial